이 논문에서는 느리게 Voltage를 가하는 형식을 dynamically하게 적용하여, SSD의 endurance를 높이는 방법을 제시한다.

여기서 endurance는 cell의 maximum P/E Cycles로 정의한다.

- WAF

- Write Amplification

- FTL의 효율성을 따지는 것으로 이해해도 좋다.

- Write Amplification

- C

- Total capcity of Flash storage

- Wday

- Write Volume

- 이를 줄이는 기존의 방식들

- Data de-duplication

- Data compression

- Write traffic throttling

- 데이터를 쓰는 작업을 제한을 두는 방식

- 열 관리

- 내구성 보호

- 성능 최적화 가능

이 연구의 목표는, MAX P/E Cycle을 improve하는 것이다.

이 연구의 key intuition은 endurance degradation에 있어서 NAND device physics model에서 착안했다.

erase voltage가 NAND endurance에 큰 영향을 미친다.

- 낮은 전압으로 천천히 NAND block을 지우는 것

NAND device가 여러 가지 타입의 write and erase mode를 support 하고, dynamically하게 펌웨어/소프트웨어 단에서 가장 적절한 mode를 선택할 수 있게 한다.

NAND cell의 tunneling oxide가 stress voltage로 인해 얇아지거나 하면 제기능 상실

→ endurance degradation으로 이어짐

느리게 지우든 뭘 하든, 우선 임계전압분포 (threshold voltage distribution)가 좁을수록 데이터를 정확히 읽을 수 있다.

낮은 전압으로 블록을 지우고 거기에 데이터를 쓰려면, 임계전압분포를 좁게 해야 하는 시간이 추가로 걸린다.

→ 데이터를 정확히 쓰기 위해 시간이 더 걸린다.

확실히 erase voltage를 처음에 14V 정도로 강하게 거는거보다, 천천히 증가시키는 방향으로 voltage를 거는게 endurance에 이득이 된다.

→ 허나 erase time이 오래 걸림.

예시로, 14V로 거는거보다 10V로 걸고 천천히 올리는게 max P/E cycle은 17% 늘어났으나, 실행 시간이 3배가 됨…

firmware단에서 이 두 가지 tradeoff를 상쇄하려고 한 게 바로 이 연구다.

- 실제 작업 단에서는 항상 SSD의 최대 성능을 바라고 동작하지는 않는다.

- write request 사이의 idle time에 block의 임계전압 폭을 줄이는 task를 수행한다.

- 그렇게, 적은 전압으로 지워진 블록을 더 자주 사용할 수 있게 한다.

→ 만약의 idle time이 얼마인지 추정이 가능하다면? 더 느리게 써서 수명을 더 가져갈 수 있지 않겠느냐?

그래서 적합한 속도의 지우기 mode를 펌웨어가 고르면 되지 않겠느냐?

그래서 새로운 형태의 FTL을 만듦

→ DPES-aware FTL : autoFTL

현재 어떤 칩도 FTL 펌웨어가 dynamically하게 voltage를 조절하게 하지 않기 때문에, FlashBench emulation 환경에서 autoFTL을 만들어서 실험했다.

여러 알려진 I/O trace들을 가지게 실험, 비교했다. 단 2.2%의 throughput만 떨어뜨리면서 max P/E cycles 수는 61.2% 향상시켰다.

보통 설계자들이 최악의 구동 상황을 가정하여 각 parameter들을 설정하고, 설계 이후엔 이 Param을 굳이 바꾸지 않는다.

허나 이러한 tradeoff 관계 등을 이용하면 원하는 결과 쪽으로 유도할 수 있다.

DPES의 경우 Wpi를 희생하여 endurance를 챙겼다.

ISPP (Incremental Step Purse Programming) scheme

- V ISPP만큼 메모리 셀들의 전압을 천천히 올림.

- 각 셀이 원하는 region의 전압이 가해졌다면, 다음 loop에서는 제거하여 관리

임계전압분포를 좁게 하여 (Wpi 감소) 데이터를 좀 더 명확히 읽고 쓰게 하기 위해서는, 증가시키는 V ISPP도 당연히 감소하여 좀 더 세밀해야 하고, 이러면 증가량이 적어져서 T Prog 시간도 증가하게 된다.

NAND Flash memory의 reliability는 보통 oxide reliability와 직결된다.

- 데이터를 산화물 층에 저장한다 (oxide layer) 전자가 이동

- 전자가 tunneling 되는 것을 막는 절연층 역할

- 근데 이 산화물 층이 약해지거나 해서 tunneling이 발생하면

- 전자가 외부로 흘러나가서 데이터가 제대로 저장이 안된다.

- 온도도 높아지면 더 심해짐

- 마모 되는 것.

erase time이 program time보다 100배 이상 긺

- 셀을 완전히 리셋시키는데 시간이 더 필요하기 때문

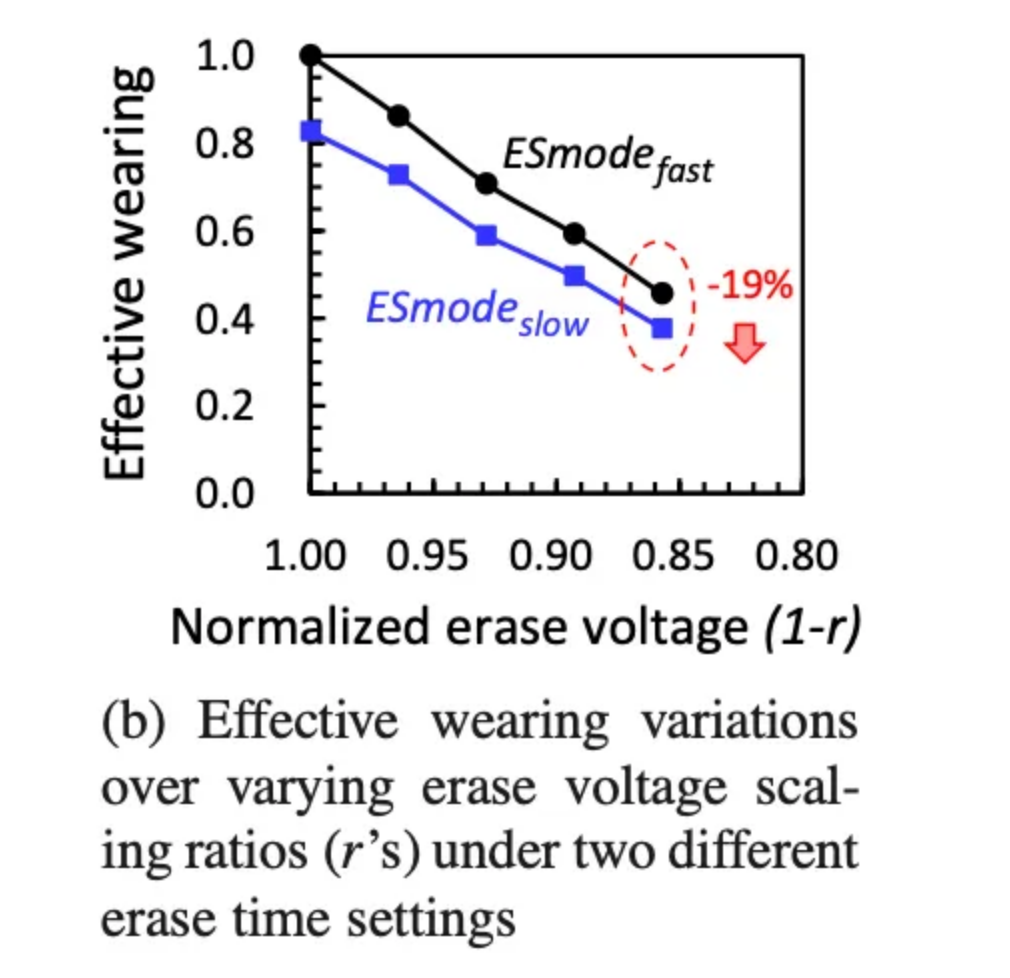

r이 높을수록 낮은 erase voltage를 의미함

BER (bit error rate) 로, 데이터 보존 정도를 보는 그래프임

역시 낮은 erase voltage일수록 BER 값이 낮은 것을 볼 수 있고, 그에 따라 P/E Cycle도 커짐

이 paper에서는 5가지의 erase write mode를 상정한다.

물론 실제 manufacturer 들을 컨택해서 확인할 수는 없지만,

실험결과가 FN-tunneling mechanism을 사용하는 미래의 NAND device 실험에 도움이 될 거라고 생각한다.

3D NAND device도 어쨌든 근간이 FN-tunneling mechanism이니..

낮은 전압으로 NAND block이 지워지면, 임계전압 window 크기가 작아진다.

임계전압분포 폭이 적어졌고, 거기에 따라 데이터를 기록하려면 더 세밀히 전압을 조정해야 하므로 program time도 같이 증가한다.

제안하는 DPES 테크닉에서는 EVmode 0 ~ 4로 5가지 mode를 설계한다.

EVmode0가 가장 높은 전압으로 지우는 모드이다.

이 때 셀이 지워지고 다시 program되려고 할 때, 약간의 Interval time이 필요하고, 그건 Mode마다 다르다.

→ 줄어든 window만큼의 폭으로 임계전압분포 폭을 줄이기 위한 시간

낮은 전압으로 지운 블록일 수록 이 기다려야 하는 시간이 길 것이다.

확실히 낮은 전압으로 천천히 지울수록, 오히려 program time이 2배까지도 증가하는 모습을 보인다.

이러한 program time requirement를 만족시키기 위해 5가지의 write mode를 또 정의한다.

Wmode4가 가장 낮은 전압인 EVmode4로 돌린 상황에서의 Write mode를 의미한다.

낮은 전압으로 지울수록 V ISPP가 높게 scaling되어 감소한다.

대신 그만큼 program time이 증가하는 trade off가 존재한다.

Effective wearing(낮을수록 좋음)이 낮아질 때 M pi도 같이 줄일 수 있다.

- 임계 전압 차이

임계 전압이 0V 인 상황

- 지우기 전압 14V가 들어오면 그냥 14V가 셀에 걸림

임계 전압이 4V인 상황

- 지우기 전압 14V가 들어오면 총 18V가 셀에 걸림

천천히 ISPE로 올리다 보면 전하가 셀 밖으로 빠져나감 (Starting voltage가 낮을수록 cell에 더 안전)

슬로우 지우기 모드는 지우기 전압을 낮추거나 시간 자체를 길게 할당해서 내구성을 확보하는 방법이 있다.

허나 너무 전압을 낮추게 되면 time이 길어지게 되고, 쓰기 throughput에 큰 영향을 미친다. 따라서 intensive한 workload에서는 이 방법을 사용할 수 없다.

EVMode(i) 가 적용된 nand block을 program 할 때는 Wmode(j, j>i)를 사용한다. (더 넉넉한 program time)

너무 lazy하게 적으면 손해니까, 적절히 write request 들어오는걸 estimate 해서 펌웨어가 잘 골라보도록 만들어보자!

우선 Effective wearing은 erasing voltage와 time에 거의 선형적으로 의존한다.

Saved threshold voltage margin은 각 write mode와 Mpi scaling ratio의 조합으로 계산할 수 있다.

→ 때문에 각 Saved threshold voltage margin에 대한 Effective wearing도 선형적으로 계산되어질 수 있다.

이 논문에서 실험은 20 nm-node NAND chip으로 실험.

기본 AutoFTL의 overview 설명

mapping table에 per block mode information과 NAND setting information을 저장해놓는다.

logical to physical mapping 정보도 담아놓는다.

Per-block mode tracking 정보

- current write mode

- total sum of the effective wearing for each block

NAND Setting table (autoFTL과 NAND Chip 사이 interface)

- 선택된 write erase mode에 적절한 device setting을 선택한다.

autoFTL은 또한 gc와 wear leveler가 DPES-aware 하게 한다.

반도체 기술의 한계로, 요새는 시스템 소프트웨어와 NAND chips 사이의 cross-layer optimization이 필요하다.

Device setting interface는 public하게 공개되어 있다!

- 읽기 작업의 reference voltage를 알 수 있다.

- 사용자가 장치 설정을 좀 더 유연하게 할 수 있게 한다.

- ONFI

- Open NAND Flash Interface

- 좀 더 모니터링 하기 쉽게 지원

DPES Manager에서 WMode를 선택하기 위해, Write request 사이의 idle time을 고려한다.

Wmode selector는 simple circular buffer를 사용한다.

circular buffer 안에는 이제 write request들이 incoming 하는 중이다.

Per-block table은 5개의 linked list를 저장한다.

이 때 5개인 이유는 각기 다른 5개의 Erase voltage mode를 적용한 block들을 들고 있기 위함이다.

알맞게 Locate 시킨 후, NAND Chip에게 적절한 Device setting을 알려준다.

- ISPP/ISPE voltages

- the erase voltage

- reference voltages for read/verify operations

이로써, read 할때 다른 write mode는 각기 다른 reference voltage를 필요로 하는데,

NAND Chip이 read를 시행하기 전에 read references를 바꿀 수 있게 한다.